RELEASE A DATA SHEET

## **FEATURES**

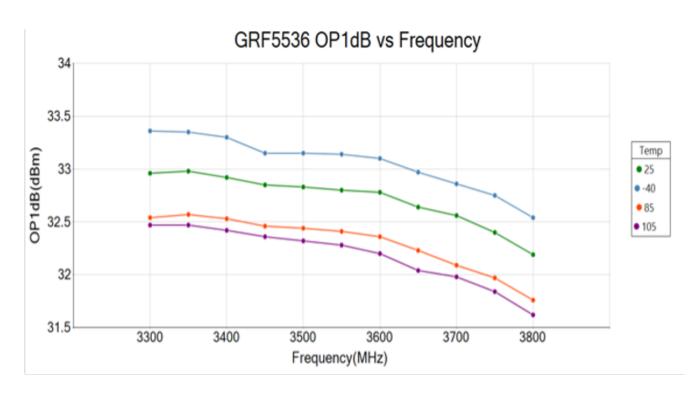

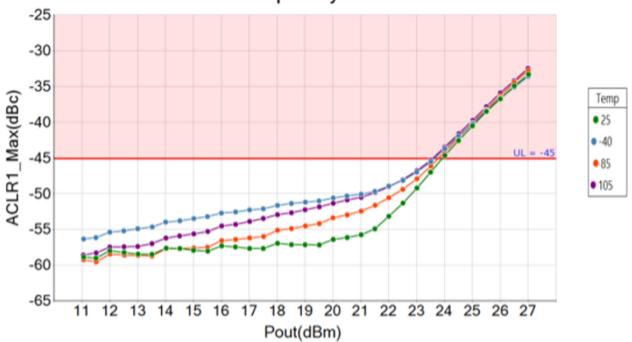

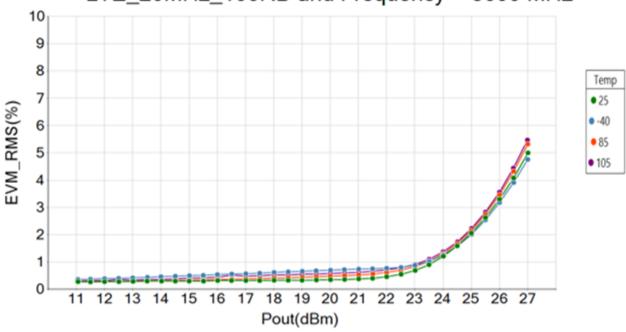

- Excellent OP1dB, OIP3, ACLR and IM3 Performance

- Native Linearity Provides up to +23 dBm P<sub>OUT</sub> with > 45 dBc

ACLR Without the Need for Digital Predistortion Correction

- +23 dBm Linear Output Power Maintained at 105 °C

- Flexible Biasing Provides Latitude for Linearity Optimization

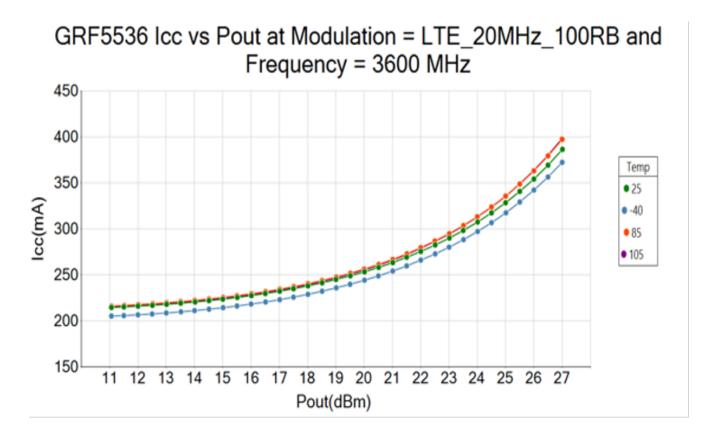

- 205 mA Native Mode Quiescent Current Consumption

- 5 V Supply Voltage

- $\bullet$  50  $\Omega$  Single-ended Input and Output Impedances

- Digital Shutdown

- Rugged Design is Extremely Resilient to Mismatched Loads

- -40 to 105 °C Operating Temperature Range

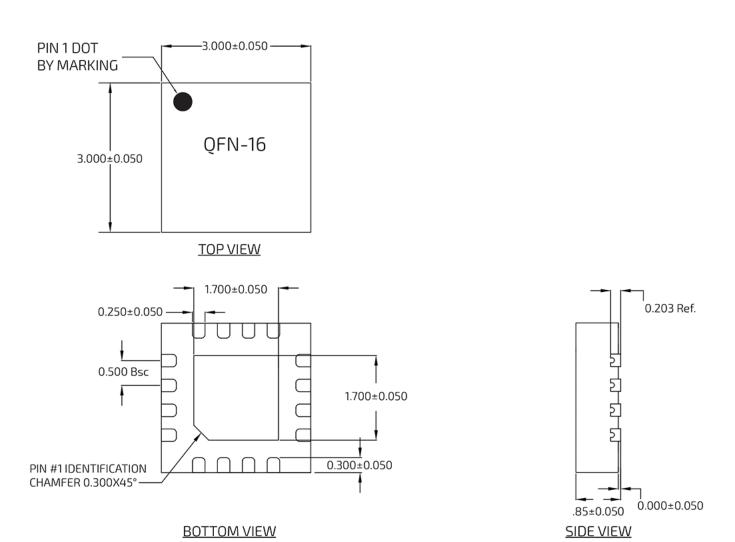

- Compact 3 x 3 mm QFN-16 Package

### Reference: 5 V / 205 mA I<sub>CCQ</sub> / 3.55 GHz

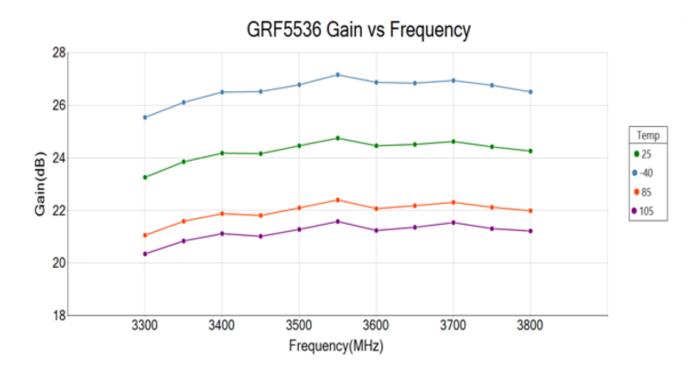

• Gain: 24.8 dB

• OIP3: 47.8 dBm @ 23 dBm POUT/tone

OP1dB: 32.6 dBmNoise Figure: 4.1 dB

### **APPLICATIONS**

- Cellular Boosters/Repeaters

- Automotive Compensators

- Picocells/Femtocells

- Cellular DAS

- Customer Premises Equipment

- Wireless Infrastructure

### **M** DESCRIPTION

The GRF5536 is a high gain, two-stage InGaP HBT power amplifier designed to deliver excellent P1dB, ACLR and IM3 performance over the standard 3.3 to 3.8 GHz band. Its exceptional native linearity makes it an ideal choice for transmitter applications that typically do not employ digital predistortion correction schemes.

An extended bandwidth tune covering 3.3 to 4.2 GHz is available. Additional tunes can be found on the GRF5536 "Custom Tunes" product page: <a href="https://great.org/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/great/gr

This device is part of a complete family of externally matched linear amplifiers that cover the following frequency ranges:

GRF5506: 0.66 - 0.72 GHz GRF5518: 1.8 - 2.0 GHz GRF5507: 0.7 - 0.91 GHz GRF5519: 1.92 - 2.2 GHz GRF5508: 0.777 - 0.96 GHz GRF5521: 2.11 - 2.17 GHz GRF5510: 0.88 - 0.96 GHz GRF5526: 2.2 - 2.7 GHz GRF5517: 1.6 - 1.92 GHz GRF5536: 3.3 - 4.2 GHz

Please consult with the GRF applications engineering team for custom tuning/evaluation board data.

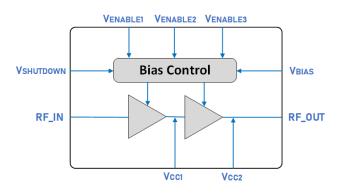

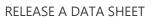

## **M** BLOCK DIAGRAM

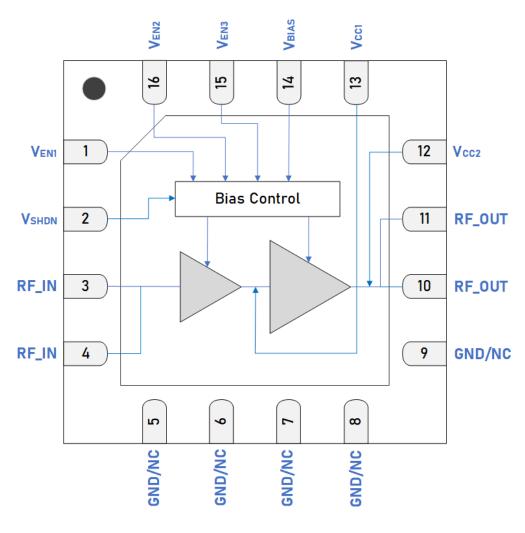

Pin Out (Top View)

# **Pin Assignments**

| Pin           | Name              | Description           | Note                                                                                                                                                                                                                                |

|---------------|-------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | V <sub>EN1</sub>  | Enable1 Voltage Input | $V_{\text{EN1}}$ and series resistor sets lccq for the output stage. $V_{\text{EN1}} \leq 0.2$ volts disables stage 1.                                                                                                              |

| 2             | $V_{SHDN}$        | Digital Shutdown Pin  | $V_{SHDN} \ge 1.7 \text{ V (Logic HIGH) disables device. } V_{SHDN} \le 0.9 \text{ V}$ (Logic LOW) enables device.                                                                                                                  |

| 3, 4          | RF_IN             | RF Input              | Pins 3 & 4 tied together on system board. An external DC blocking cap must be used.                                                                                                                                                 |

| 5, 6, 7, 8, 9 | GND/NC            | Ground or No Connect  | No internal connection to die. These pins can be left unconnected, or be connected to ground (recommended). Use a via as close to the pin as possible if grounded.                                                                  |

| 10, 11        | RF_OUT            | PA Output             | Pins 10 & 11 tied together on system board.                                                                                                                                                                                         |

| 12            | V <sub>CC2</sub>  | Bias Voltage          | V <sub>CC2</sub> must be applied to this pin via an RF choke.                                                                                                                                                                       |

| 13            | V <sub>CC1</sub>  | Bias Voltage          | $V_{\text{CC1}}$ must be applied to this pin via L-C interstage match.                                                                                                                                                              |

| 14            | V <sub>BIAS</sub> | Bias Circuit Supply   | Connect to V <sub>CC2</sub> through an external resistor.                                                                                                                                                                           |

| 15            | V <sub>EN3</sub>  | Enable3 Voltage Input | Bias Voltage applied via series resistor.                                                                                                                                                                                           |

| 16            | V <sub>EN2</sub>  | Enable2 Voltage Input | $V_{EN2}$ and series resistor set lccq for the output stage. $V_{EN2} \le 0.2 \text{ V}$ disables stage 2.                                                                                                                          |

| PKG BASE      | GND               | Ground                | Provides DC and RF ground for the amplifier, as well as thermal heat sink. Recommend multiple 8 mil vias beneath the package for optimal RF and thermal performance. Refer to evaluation board top layer graphic on schematic page. |

**Note 1:** GRF5526 and GRF5536 have a common pinout that is slightly different from the pinout shared by all the other GRF55XXW PAs. Please see page 2.

# **Absolute Ratings**

| Parameter                                                   |                                                                                                                  | Symbol                    | Min. | Max.   | Unit |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------|------|--------|------|

| Supply Volta                                                | ge                                                                                                               | V <sub>cc</sub>           | 4    | 5.5    | V    |

| DC Inquit                                                   | 50 $\Omega$ , $V_{CC} = 5$ V, CW Tone, 100% Duty Cycle, $T_{PKG BASE} = 25$ °C.                                  |                           |      | 20     |      |

| RF Input<br>Power                                           | Load VSWR $\leq$ 8:1, all phase angles, $V_{CC} = 5$ V, CW Tone, 100% Duty Cycle, $T_{PKG BASE} = -40$ to 105°C. | P <sub>IN MAX</sub> - 8:1 |      | 17     | dBm  |

| Operating Te                                                | emperature (Package Base).                                                                                       | T <sub>PKG BASE</sub>     | -40  | 105    | °C   |

| Maximum Ju<br>Hours).                                       | nction Temperature (MTTF > 106                                                                                   | T <sub>J MAX</sub>        |      | 170    | °C   |

| Maximum Dissipated Power (Stage 1). DC only. No RF applied. |                                                                                                                  | P <sub>DISS MAX</sub>     |      | * 360  | mW   |

| Maximum Dissipated Power (Stage 2). DC only. No RF applied. |                                                                                                                  | P <sub>DISS MAX</sub>     |      | * 1250 | mW   |

| Shutdown Voltage                                            |                                                                                                                  | V <sub>SHDN</sub>         |      | ** 5.5 | V    |

<sup>\*</sup> Bias resistors M2/M4 have been empirically optimized for linearity. Thus, there will be no benefit in decreasing resistance (thereby increasing Icco).

Said linear relationship can be used to scale M1 for higher Vshdn voltage: use pin condition Vshdn\_pin/Ishdn =  $2.2V/146\mu$ A. Calculate M1 for Vshdn/Ishdn =  $5V/146\mu$ A: M1 = (5-2.2)/(0.000146) =  $19.2 \text{ k}\Omega$ .

<sup>\*\*</sup> With M1 = 0  $\Omega$ , Ishdn increases linearly from Vshdn/Ishdn = 1.8V/82 $\mu$ A to 4.2V/498 $\mu$ A.

**RELEASE A DATA SHEET**

## **Absolute Ratings (continued)**

## **Electrostatic Discharge**

| Human Body Model | НВМ | 1000 |  | V |  |

|------------------|-----|------|--|---|--|

|------------------|-----|------|--|---|--|

### **Storage**

| Storage Temperature        | T <sub>STG</sub> | -65 | 150 | °C |

|----------------------------|------------------|-----|-----|----|

| Moisture Sensitivity Level | MSL              |     | 1   |    |

**Caution! ESD Sensitive Device.**

**Exceeding Absolute Maximum Rating conditions may cause permanent damage.**

Note: For additional information, please refer to Manufacturing Note MN-001 - Packaging and Manufacturing Information.

All Guerrilla RF products are provided in RoHS compliant lead (Pb)-free packaging. For additional information, please refer to the Certificate of RoHS Compliance.

# **Recommended Operating Conditions**

| Parameter                               | Symphol               | Sp   | ecificati | ion  | Unit | Condition                                                                        |  |

|-----------------------------------------|-----------------------|------|-----------|------|------|----------------------------------------------------------------------------------|--|

| Parameter                               | Symbol                | Min. | Тур.      | Max. | Onic |                                                                                  |  |

| Supply Voltage                          | V <sub>CC</sub>       | 4    | 5         | 5.5  | V    |                                                                                  |  |

| Operating Temperature<br>(Package Base) | T <sub>PKG BASE</sub> | -40  |           | 105  | °C   |                                                                                  |  |

| DE Fraguency Pange                      | F <sub>RF</sub>       | 3.3  |           | 3.8  | GHz  | Typical application schematic using the 3.3 to 3.8 GHz tuning set (notes 2 & 3). |  |

| RF Frequency Range                      | F <sub>RF</sub>       | 3.3  |           | 4.2  | GHz  | Typical application schematic using the 3.3 to 4.2 GHz tuning set (notes 2 & 3). |  |

| RF_IN Port Impedance                    | $Z_{RFIN}$            |      | 50        |      | Ω    | Single ended with 2-element match.                                               |  |

| RF_OUT Port Impedance                   | Z <sub>RFOUT</sub>    |      | 50        |      | Ω    | Single ended with 2-element match.                                               |  |

**Note 2:** Operation outside of this range is supported by using different custom tunes. Examples of other optimized tunes can be found here: <u>GRF5536 Custom Tunes</u>

**Note 3:** Contact the Guerrilla RF Applications team for guidance of optimizing the tuning of the device for alternative bands.

# **Nominal Operating Parameters - General**

The following conditions apply unless noted otherwise: typical application schematic using the 3.3 to 3.8 GHz tuning set. M2 = 6040  $\Omega$ , M4 = 3570  $\Omega$ , M10 = 1200  $\Omega$ , V<sub>SHDN</sub> = LOW, V<sub>CC</sub> = +4.75 to +5.25 V, I<sub>CCQ</sub> = 205 mA, P<sub>OUT</sub> = +23 dBm, F<sub>TEST</sub> = 3.55 GHz, T<sub>PKG BASE</sub> = -40 to +105 °C. Typical values: V<sub>CC</sub> = 5 V, I<sub>CCQ</sub> = 205 mA, P<sub>OUT</sub> = +23 dBm, F<sub>TEST</sub> = 3.55 GHz, T<sub>PKG BASE</sub> = 25 °C. 50  $\Omega$  system impedance, Evaluation board losses are included within the specifications.

| Parameter                      | Symbol                | Specification |      |                 | Unit | Condition                                                          |  |

|--------------------------------|-----------------------|---------------|------|-----------------|------|--------------------------------------------------------------------|--|

|                                |                       | Min.          | Тур. | Max.            |      |                                                                    |  |

| Supply Quiescent Current       | I <sub>ccq</sub>      |               | 205  |                 | mA   | I <sub>CCQ1</sub> + I <sub>CCQ2</sub> . No RF applied.             |  |

| Supply Current with RF Applied | I <sub>cc</sub>       |               | 280  |                 | mA   | $I_{CC1} + I_{CC2}$ . RF applied. $P_{OUT} = 23$ dBm.              |  |

| Enable Current 1               | I <sub>ENABLE1</sub>  |               | 0.18 |                 | mA   | V <sub>CC</sub> = 5 V, T <sub>PKG</sub> HEAT SINK = 25 °C.         |  |

| Enable Current 2               | I <sub>ENABLE2</sub>  |               | 0.49 |                 | mA   | V <sub>CC</sub> = 5 V, T <sub>PKG HEAT SINK</sub> = 25 °C.         |  |

| Enable Current 3               | I <sub>ENABLE3</sub>  |               | 0.8  |                 | mA   | $V_{CC} = 5 \text{ V}, T_{PKG \text{ HEAT SINK}} = 25 \text{ °C}.$ |  |

| Operating Temperature Range    | T <sub>PKG</sub> BASE | -40           |      | 105             | °C   | Measured on Package Base.                                          |  |

| Logic Input Low                | V <sub>IL</sub>       | 0             |      | 0.9             | V    | Applies to V <sub>SHDN</sub> Input.                                |  |

| Logic Input High               | VIH                   | 1.7           |      | V <sub>CC</sub> | V    | Applies to V <sub>SHDN</sub> Input.                                |  |

| Logic Current Low              | lIL                   |               | 3    |                 | nA   | Applies to $V_{SHDN}$ Input. $V_{IL} = 0.9 V$ .                    |  |

| Logic Input High               | l                     |               | 82   |                 |      | Applies to $V_{SHDN}$ Input. $V_{IH} = 1.8 \text{ V}$ .            |  |

| Logic Input High               | IH                    |               | 322  |                 | μΑ   | Applies to $V_{SHDN}$ Input. $V_{IH} = 3.3 \text{ V}$ .            |  |

| Switching Rise Time            | T <sub>RISE</sub>     |               | 150  |                 | ns   | Applies to V <sub>SHDN</sub> Input.                                |  |

| Switching Fall Time            | T <sub>FALL</sub>     |               | 10   |                 | ns   | Applies to V <sub>SHDN</sub> Input.                                |  |

#### **Disabled Mode**

| Supply Quiescent Current | I <sub>CCQ-SHDN</sub>     | 240 | μΑ | $V_{CC} = 5 \text{ V}, V_{SHDN}/V_{EN1}/V_{EN3} = \text{HIGH}$                      |

|--------------------------|---------------------------|-----|----|-------------------------------------------------------------------------------------|

| Enable Current 1         | I <sub>ENABLE1-SHDN</sub> | 0.5 | mA | V <sub>CC</sub> = 5 V, V <sub>SHDN</sub> /V <sub>EN1</sub> /V <sub>EN3</sub> = HIGH |

| Enable Current 2         | I <sub>ENABLE2-SHDN</sub> | 1.1 | mA | $V_{CC} = 5 \text{ V}, V_{SHDN}/V_{EN1}/V_{EN3} = \text{HIGH}$                      |

| Enable Current 3         | I <sub>ENABLE3-SHDN</sub> | 3.3 | mA | $V_{CC} = 5 \text{ V}, V_{SHDN}/V_{EN1}/V_{EN3} = \text{HIGH}$                      |

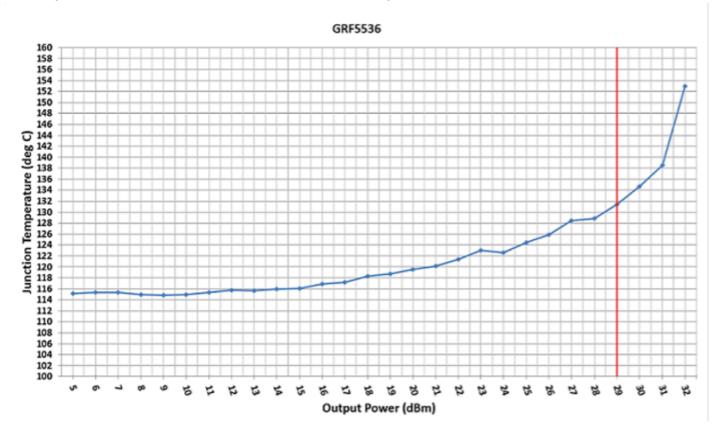

#### **Thermal Data**

| See plot of Junction<br>Temperature vs. Output Power. |  |  |  |  |  | On standard evaluation board. |  |

|-------------------------------------------------------|--|--|--|--|--|-------------------------------|--|

|-------------------------------------------------------|--|--|--|--|--|-------------------------------|--|

# **Nominal Operating Parameters - RF**

The following conditions apply unless noted otherwise: Typical Application Schematic using the 3.3 to 3.8 GHz tuning set. M2 =  $6040~\Omega$ , M4 =  $3570~\Omega$ , M10 =  $1200~\Omega$ , V<sub>SHDN</sub> = LOW, V<sub>CC</sub> = +4.75 to +5.25 V, I<sub>CCQ</sub> = 205 mA, P<sub>OUT</sub> = +23 dBm, F<sub>TEST</sub> = 3.55 GHz, T<sub>PKG BASE</sub> = -40 to +105~°C. Typical values: V<sub>CC</sub> = 5 V, I<sub>CCQ</sub> = 205 mA, P<sub>OUT</sub> = +23 dBm, F<sub>TEST</sub> = 3.55 GHz,  $50~\Omega$  system impedance, T<sub>PKG BASE</sub> = 25~°C. Evaluation board losses are included within the specifications.

| Parameter                        | Symbol              | Specification |       |      | Unit | Condition                                                                                                                                                                            |  |

|----------------------------------|---------------------|---------------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                        | Symbol              | Min.          | Тур.  | Max. | Onit | Condition                                                                                                                                                                            |  |

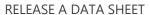

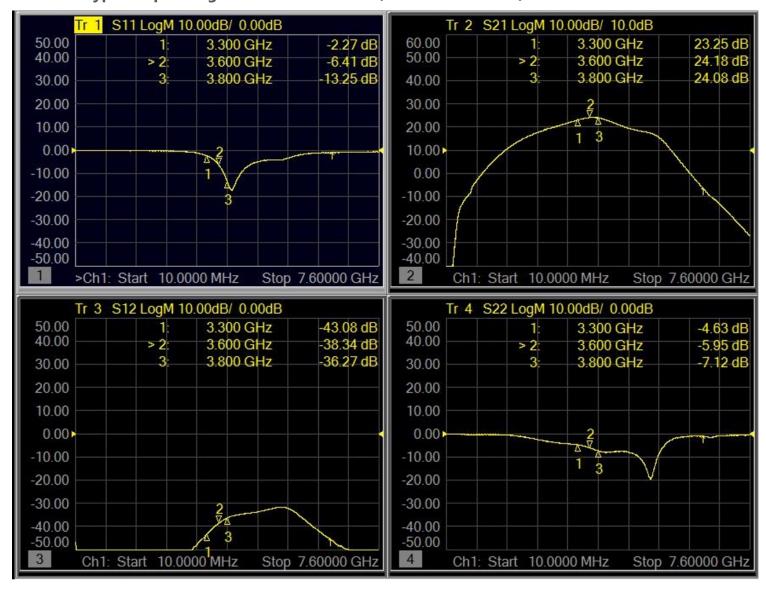

| Small Signal Gain                | S21                 | 22.5          | 24.8  |      | dB   | LTE 20MHz 100RB TM1.1  Downlink Waveform with 9.8  dB PAR, F <sub>TEST</sub> = 3.6 GHz, T <sub>PKG</sub> BASE = 25 °C, Vcc = 5 V, PIN = -25 dBm.                                     |  |

| Standby Mode Gain                | S21 <sub>STBY</sub> |               | -45   |      | dB   | Disabled Mode, LTE 20MHz 100RB TM1.1 Downlink Waveform with 9.8 dB PAR, $V_{SHDN}/V_{EN1}/V_{EN2} = HIGH, P_{IN} = 0 dBm.$                                                           |  |

| Input Return Loss                | S11                 |               | < -2  |      | dB   | F <sub>RF</sub> = 3.3 to 3.8 GHz.                                                                                                                                                    |  |

| Output Return Loss               | S22                 |               | < -4  |      | dB   | F <sub>RF</sub> = 3.3 to 3.8 GHz.                                                                                                                                                    |  |

| Reverse Isolation                | S12                 |               | < -34 |      | dB   | F <sub>RF</sub> = 3.3 to 3.8 GHz.                                                                                                                                                    |  |

| Noise Figure                     | NF                  |               | 4.1   |      | dB   | On standard evaluation board.                                                                                                                                                        |  |

| Output 3rd Order Intercept Point | OIP3                |               | 47.8  |      | dBm  | +23 dBm P <sub>OUT</sub> per tone at 600 kHz spacing.                                                                                                                                |  |

| Output 1 dB Compression Power    | OP1dB               |               | 32.8  |      | dBm  | Sine wave input, $V_{CC} = 5 \text{ V}$ , $T_{PKG BASE} = 25 \text{ °C}$ .                                                                                                           |  |

| <sup>2nd</sup> Harmonic          | 2f <sub>0</sub>     |               |       | -22  | dBc  | P <sub>OUT</sub> = 26 dBm <b>(note 4)</b> .                                                                                                                                          |  |

| 3rd Harmonic                     | 3f <sub>0</sub>     |               |       | -45  | dBc  | P <sub>OUT</sub> = 26 dBm <b>(note 4)</b> .                                                                                                                                          |  |

| Adjacent Channel Leakage Ratio   | ACLR                |               | -48   |      | dBc  | P <sub>OUT</sub> = +23 dBm. LTE 20MHz<br>100RB TM1.1 Downlink<br>Waveform with 9.8 dB PAR,<br>F <sub>TEST</sub> = 3.55 GHz, T <sub>PKG BASE</sub> = 25<br>°C, V <sub>CC</sub> = 5 V. |  |

**Note 4:** MIN/MAX limits defined using *modeled estimates* that account for part-to-part variations and expected process spreads. As additional production lots are fabricated, accumulated test data will be used to refine the MIN/MAX limits.

## **GRF5536 Typical Operating Curves: 3.3 to 3.8 GHz Tune**

**GRF5536 Typical Operating Curves: ACLR vs. Pout (LTE 20Q100RB TM1.1 9.8 dB PAR)**

# GRF5536 ACLR1 vs Pout at Modulation = LTE\_20MHz\_100RB and Frequency = 3600 MHz

**GRF5536 Typical Operating Curves:** Stage 1 + Stage 2 I<sub>CC</sub> vs. P<sub>OUT</sub> (LTE 20Q100RB TM1.1 9.8 dB PAR)

**GRF5536 Typical Operating Curves: EVM vs. POUT (LTE 20Q100RB TM1.1 9.8 dB PAR)**

# GRF5536 EVM\_RMS vs Pout at Modulation = LTE\_20MHz\_100RB and Frequency = 3600 MHz

# **S3F**

### **GRF5536 Typical Operating Curves: S-Parameters (3.3 to 3.8 GHz Tune)**

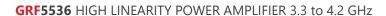

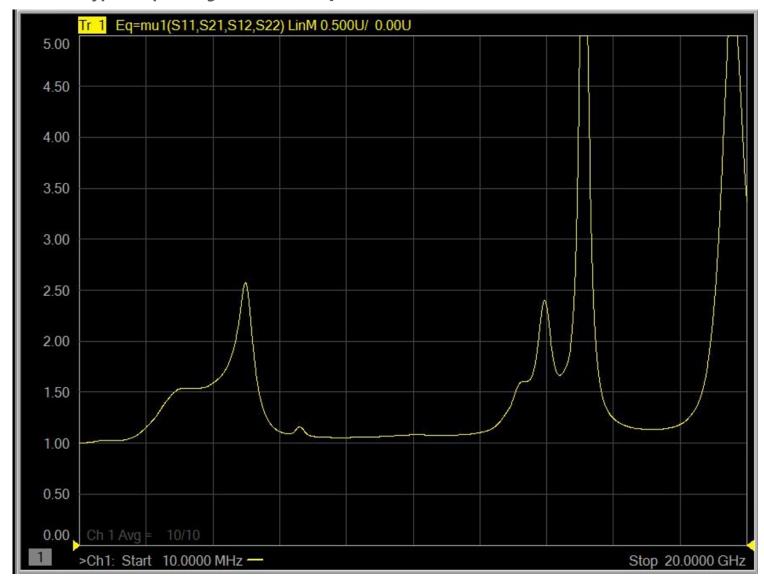

## **GRF5536 Typical Operating Curves: Stability Mu (10 MHz to 20 GHz)**

Note: Mu factor ≥ 1.0 implies unconditional stability.

RELEASE A DATA SHEET

## **GRF5536 Typical Operating Curves: Junction Temperature (per application schematic @ 85 °C)**

GRF5536, being a 2-stage device, sees one of the stages governing junction temperature over power sweep. Red line = 29 dBm shows where T J is equivalent in both stages. At left of red line, stage 2 governs TJ (Q2 TJ is higher). To the right of red line, stage 1 governs TJ (Q1 TJ is higher).

Setting bias resistor M2/M4 per application schematic ensures best linearity and yields thermal performance shown in the plot. If the application does not require high IMD3/ACLR linearity, bias resistor can be adjusted higher. This will lower bias point(s) and junction temperature will be contained within/below that shown in the plot.

## **Truth Table**

| Pin               | Logic | Condition             |  |  |  |

|-------------------|-------|-----------------------|--|--|--|

| V.                | LOW   | Full Operation        |  |  |  |

| V <sub>SHDN</sub> | HIGH  | All Amplifiers Off    |  |  |  |

| \/                | LOW   | Stage 1 Amplifier Off |  |  |  |

| V <sub>EN1</sub>  | HIGH  | Stage 1 Amplifier On  |  |  |  |

| \/ .              | LOW   | Stage 2 Amplifier Off |  |  |  |

| V <sub>EN2</sub>  | HIGH  | Stage 2 Amplifier On  |  |  |  |

| \/ .              | LOW   | Stage 2 Amplifier Off |  |  |  |

| V <sub>EN3</sub>  | HIGH  | Stage 2 Amplifier On  |  |  |  |

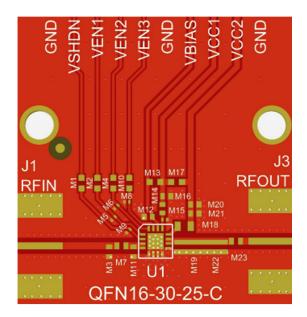

**GRF5536 Standard Evaluation Board Schematic**

**GRF5536 Evaluation Board Assembly Diagram**

## **GRF5536 Evaluation Board Assembly Diagram Reference**

| Component        | Туре              | Manufacturer | Family | Value    | Package Size | Substitution |

|------------------|-------------------|--------------|--------|----------|--------------|--------------|

| M1               | Resistor          | Various      | 5%     | 0 Ω      | 0402         | ok           |

| M2               | Resistor          | Various      | 1%     | 6040 Ω   | 0402         | ok           |

| M4               | Resistor          | Various      | 1%     | 3570 Ω   | 0402         | ok           |

| M7               | Capacitor         | Murata       | GJM    | 0.7 pF   | 0402         | ok           |

| M9               | Capacitor         | Murata       | GJM    | 10 pF    | 0201         | ok           |

| M10              | Resistor          | Various      | 1%     | 1200 Ω   | 0402         | ok           |

| M11              | Capacitor         | Murata       | GJM    | 0.8 pF   | 0402         | ok           |

| M12              | Capacitor         | Murata       | GRM    | ** 10 μF | 0402         | ok           |

| M13              | Resistor (jumper) | Various      | 5%     | 0 Ω      | 0402         | ok           |

| M14              | Resistor          | Various      | 5%     | 0 Ω      | 0402         | ok           |

| M15              | Capacitor         | Murata       | GRM    | 0.1 μF   | 0201         | ok           |

| M16              | Capacitor         | Murata       | GRM    | ** 10 μF | 0402         | ok           |

| M17              | Resistor (jumper) | Various      | 5%     | 0 Ω      | 0402         | ok           |

| M18              | Inductor          | Murata       | LQW    | 10 nH    | 0402         | ok           |

| M19              | Capacitor         | Murata       | GJM    | 0.8 pF   | 0402         | ok           |

| M20              | Capacitor         | Murata       | GRM    | 10 μF    | 0402         | ok           |

| M21              | Capacitor         | Murata       | GRM    | 100 pF   | 0402         | ok           |

| M23              | Capacitor         | Murata       | GJM    | 10 pF    | 0402         | ok           |

| Evaluation Board | QFN16-30-25-C     |              |        |          |              |              |

**Note 5:** Standard evaluation board bias:  $V_{CC} = 5 \text{ V}$ ,  $V_{ENABLE} = 5 \text{ V}$ .

<sup>\*\*</sup> GRM155C80J106ME11D rated for 5 V @ 105 °C.

QFN 16 3x3mm Package Dimensions

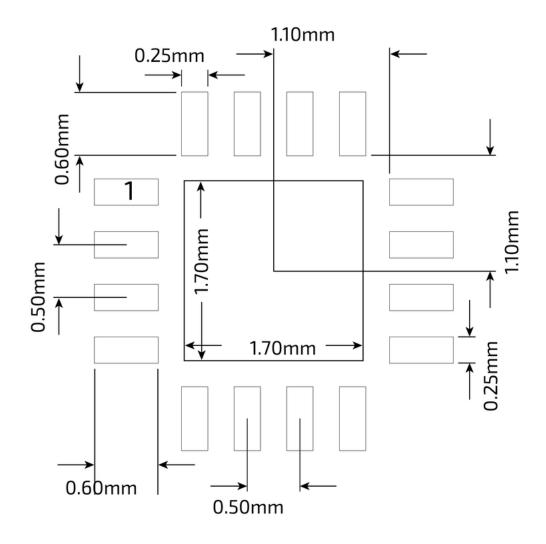

QFN 16 3x3mm Suggested PCB Footprint (Top View)

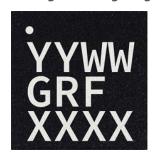

### **Package Marking Diagram**

Line 1: "YY" = Year. "WW" = WORK WEEK the Device was assembled.

Line 2: "GRF" = Guerrilla RF

Line 3: "XXXX" = Device Part Number.

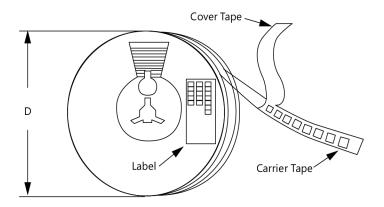

### **Tape and Reel Information**

Guerrilla RF's tape and reel specification complies with Electronics Industries Association (EIA) standards for "Embossed Carrier Tape of Surface Mount Components for Automatic Handling" (reference EIA-481). Devices are loaded with pins down into the carrier pocket with protective cover tape and reeled onto a plastic reel. Each reel is packaged in a cardboard box. There are product labels on the reel, the protective ESD bag, and the outside surface of the box. For the latest reel specifications and package information (including units/reel), please visit Package Manufacturing Information | Guerrilla RF (guerrilla-rf.com).

Tape and Reel Packaging with Reel Diameter Noted (D)

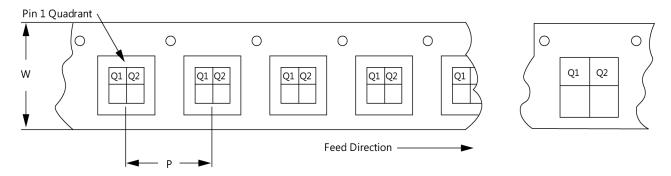

Carrier Tape Width (W), Pitch (P), Feed Direction and Pin 1 Quadrant Information

## RELEASE A DATA SHEET

## **Revision History**

| Revision Date      | Description of Change                                                                                                                                                                                                                                 |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 16, 2021  | Preliminary Data Sheet.                                                                                                                                                                                                                               |

| May 9, 2022        | Changed RF Input Power (Pin Max) from TBD to 23 dBm.                                                                                                                                                                                                  |

| August 25, 2022    | Upgraded Evaluation Board Layout from RevB to RevC. Changed C1 to M12 on Evaluation Board BOM and Schematic.                                                                                                                                          |

| October 3, 2022    | Added Thermal Resistance specification.                                                                                                                                                                                                               |

| November 8, 2022   | Added characterization plots. Added new S-parameter and Mu plots. Updated evaluation board BOM.                                                                                                                                                       |

| December 22, 2022  | Lowered Gain specification from 27.3 to 24.5 dB.                                                                                                                                                                                                      |

| January 27, 2023   | Absolute Ratings Table: Added the following condition to Maximum Dissipated Power for Stage 1 & 2: DC only. No RF applied. Changed Stage 1 Maximum Dissipated Power from TBD to 500 mW. Changed Stage 2 Maximum Dissipated Power from TBD to 1400 mW. |

| February 28, 2023  | Added new Characterization Plots. Updated BOM.                                                                                                                                                                                                        |

| June 7, 2023       | Release Ø Data Sheet.                                                                                                                                                                                                                                 |

| September 19, 2023 | Release A Data Sheet.                                                                                                                                                                                                                                 |

| October 12, 2023   | Added 2nd and 3rd Harmonics.                                                                                                                                                                                                                          |

| July 25, 2024      | Upgraded Data Sheet to new format only.                                                                                                                                                                                                               |

| February 14, 2025  | Corrected typo on page-7 (condition for Supply Quiescent Current and Supply Current).                                                                                                                                                                 |

| May 21, 2025       | Updated frequency of family of part numbers listed on page 1.                                                                                                                                                                                         |

RELEASE A DATA SHEET

#### **Data Sheet Classifications**

| Data Sheet Status | Notes                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance           | S-parameter and NF data based on EM simulations for the fully packaged device using foundry-supplied transistor S-parameters. Linearity estimates based on device size, bias condition and experience with related devices.                                                                                                                                                                                                      |

| Preliminary       | All data based on evaluation board measurements taken within the Guerrilla RF Applications Lab. Any MIN/MAX limits represented within the data sheet are based solely on <i>estimated</i> part-to-part variations and process spreads. All parametric values are subject to change pending the collection of additional data.                                                                                                    |

| Release Ø         | All data based on measurements taken with <i>production-released</i> material. TYP values are based on a combination of ATE and bench-level measurements, with MIN/MAX limits defined using <i>modelled estimates</i> that account for part-to-part variations and expected process spreads. Although unlikely, future refinements to the TYP/MIN/MAX values may be in order as multiple lots are processed through the factory. |

| Release A-Z       | All data based on measurements taken with production-released material derived from multiple lots which have been fabricated over an extended period of time. MIN/MAX limits may be refined over previous releases as more statistically significant data is collected to account for process spreads.                                                                                                                           |

Information in this data sheet is specific to the Guerrilla RF, Inc. ("Guerrilla RF") product identified.

This data sheet, including the information contained in it, is provided by Guerrilla RF as a service to its customers and may be used for informational purposes only by the customer. Guerrilla RF assumes no responsibility for errors or omissions on this data sheet or the information contained herein. Information provided is believed to be accurate and reliable, however, no responsibility is assumed by Guerrilla RF for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. Guerrilla RF assumes no liability for any data sheet, data sheet information, materials, products, product information, or other information provided hereunder, including the sale, distribution, reproduction or use of Guerrilla RF products, information or materials.

No license, whether express, implied, by estoppel, by implication or otherwise granted by this data sheet for any intellectual property of Guerrilla RF, or any third party, including without limitation, patents, patent rights, copyrights, trademarks, and trade secrets. All rights are reserved by Guerrilla RF.

All information herein, products, product information, data sheets, and data sheet information are subject to change and availability without notice. Guerrilla RF reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice. Guerrilla RF may further change its data sheet, product information, documentation, products, services, specifications or product descriptions at any time, without notice. Guerrilla RF makes no commitment to update any materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

GUERRILLA RF INFORMATION, PRODUCTS, PRODUCT INFORMATION, DATA SHEETS AND DATA SHEET INFORMATION ARE PROVIDED "AS IS" AND WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. GUERRILLA RF DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. GUERRILLA RF SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Customers are solely responsible for their use of Guerrilla RF products in the Customer's products and applications or in ways which deviate from Guerrilla RF's published specifications, either intentionally or as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Guerrilla RF assumes no liability or responsibility for applications assistance, customer product design, or damage to any equipment resulting from the use of Guerrilla RF products outside of stated published specifications or parameters.